This is the Revision A verion of the Digital8 module. The status of this project is finished.

# **Digital8 Module (Revision A)**

# **Table of Contents**

This document is also available in <u>PDF</u> format.

- <u>1. Introduction</u>

- <u>2. Programming</u>

- <u>3. Hardware</u>

- ◆ <u>3.1 Circuit Schematic</u>

- ◆ <u>3.2 Printed Circuit Board</u>

- <u>4. Software</u>

- <u>5. Issues</u>

## 1. Introduction

The Digital8 module provides the ability to input and output 8 bits of digital data. The direction of each bit can be changed under program control.

## 2. Programming

The programmer can download a complement mask to cause any of the bits to be complemented prior to reading.

The Digital8 module supports the <u>Interrupt Protocol</u>. The interrupt pending bit is set whenever the the formula:

```

L\&(\sim I) \mid H\&I \mid R\&(\sim P)\&I \mid F\&P\&(\sim I)]

```

is non-zero, where:

- I is the current input bits XOR'ed with the complement mask (C)

- P is the previous value of I

- L is the low mask

- H is the high mask

- R is the raising mask

- F is the falling mask

and

- ~ is bit–wise complement

- | is bit-wise OR

- & is bit-wise AND

Once the interrupt pending bit is set, it must be explicitly cleared by the user.

#### Digital8 Module (Revision A)

| Commercial                   | Send/   |   |   | E | Byte | Va | lue |   |   | Discoursion                                                                                            |

|------------------------------|---------|---|---|---|------|----|-----|---|---|--------------------------------------------------------------------------------------------------------|

| Command                      | Receive |   |   |   |      |    |     |   |   | Discussion                                                                                             |

| Read Inputs Low              | Send    | 0 | 0 | 0 | 0    | 0  | 0   | 0 | 0 | Return low order 5–bits of inpu<br><i>iiiii</i> (after XOR'ing with<br>complement mask)                |

|                              | D       | 0 | 0 | 0 |      |    |     |   |   |                                                                                                        |

|                              | Receive | 0 | 0 |   | i    | i  | i   | i | i |                                                                                                        |

| Read Inputs High             | Send    | 0 | 0 | 0 | 0    | 0  | 0   | 0 | 1 | Return high order 5–bits of<br>input <i>IIIII</i> (after XOR'ing with<br>complement mask)              |

|                              | Receive | 0 | 0 | 0 | Ι    | Ι  | Ι   | Ι | Ι |                                                                                                        |

| Read Complement<br>Mask Low  | Send    | 0 | 0 | 0 | 0    | 0  | 0   | 1 | 0 | Return low order 5-bits of complement mask <i>ccccc</i>                                                |

|                              | Receive | 0 | 0 | 0 | с    | с  | с   | с | с |                                                                                                        |

| Read Complement<br>Mask High | Send    | 0 | 0 | 0 | 0    | 0  | 0   | 1 | 1 | Return high order 5 bits of complement mask <i>CCCCC</i>                                               |

|                              | Receive | 0 | 0 | 0 | С    | С  | С   | С | С |                                                                                                        |

| Read Direction Mask<br>Low   | Send    | 0 | 0 | 0 | 0    | 0  | 1   | 0 | 0 | Return low order 5-bits of                                                                             |

|                              | Receive | 0 | 0 | 0 | d    | d  | d   | d | d | direction mask ddddd                                                                                   |

| Read Direction Mask<br>High  | Send    | 0 | 0 | 0 | 0    | 0  | 1   | 0 | 1 | Return high order 5 bits of direction mask <i>DDDDD</i>                                                |

|                              | Receive | 0 | 0 | 0 | D    | D  | D   | D | D |                                                                                                        |

| Read Raw Low                 | Send    | 0 | 0 | 0 | 0    | 0  | 1   | 1 | 0 | Return low order 5-bits of raw<br>input data <i>rrrrr</i> (without<br>XOR'ing with complement<br>mask) |

|                              | Receive | 0 | 0 | 0 | r    | r  | r   | r | r |                                                                                                        |

|                              | Send    | 0 | 0 | 0 | 0    | 0  | 1   | 1 | 1 | Return high order 5-bits of raw<br>input data <i>RRRR</i> (without<br>XOR'ing with complement<br>mask) |

| Read Raw High                | Receive | 0 | 0 | 0 | R    | R  | R   | R | R |                                                                                                        |

| Read Low Mask<br>Low         | Send    | 0 | 0 | 0 | 0    | 1  | 0   | 0 | 0 | Return low order 5–bits of low mask <i>lllll</i>                                                       |

|                              | Receive | 0 | 0 | 0 | l    | l  | l   | l | l |                                                                                                        |

| Read Low Mask<br>High        | Send    | 0 | 0 | 0 | 0    | 1  | 0   | 0 | 1 | Return high order 5–bits of low mask <i>LLLLL</i>                                                      |

|                              | Receive | 0 | 0 | 0 | L    | L  | L   | L | L |                                                                                                        |

| Read High Mask<br>Low        | Send    | 0 | 0 | 0 | 0    | 1  | 0   | 1 | 0 | Return low order 5–bits of the high mask <i>hhhhh</i>                                                  |

|                              | Receive | 0 | 0 | 0 | h    | h  | h   | h | h |                                                                                                        |

| Read High Mask<br>High       | Send    | 0 | 0 | 0 | 0    | 1  | 0   | 1 | 1 | Return high order 5 bits of the high mask <i>HHHHH</i>                                                 |

|                              | Receive | 0 | 0 | 0 | Η    | Η  | Η   | Η | Η |                                                                                                        |

| Read Raising Mask<br>Low     | Send    | 0 | 0 | 0 | 0    | 1  | 1   | 0 | 0 | Return low order 5-bits of the raising mask <i>rrrrr</i>                                               |

|                              | Receive | 0 | 0 | 0 | r    | r  | r   | r | r |                                                                                                        |

| Read Raising Mask<br>High    | Send    | 0 | 0 | 0 | 0    | 1  | 1   | 0 | 1 | Return high order 5 bits of the raising mask <i>RRRR</i>                                               |

|                              | Receive | 0 | 0 | 0 | R    | R  | R   | R | R |                                                                                                        |

| Read Falling Mask<br>Low     | Send    | 0 | 0 | 0 | 0    | 1  | 1   | 1 | 0 | Return low order 5–bits of the falling mask <i>fffff</i>                                               |

|                              | Receive | 0 | 0 | 0 | f    | f  | f   | f | f |                                                                                                        |

| Read Falling Mask<br>High    | Send    | 0 | 0 | 0 | 0    | 1  | 1   | 1 | 1 | Return high order 5–bits of the falling mask <i>FFFFF</i>                                              |

|                              | Receive | 0 | 0 | 0 | F    | F  | F   | F | F |                                                                                                        |

| Read Outputs Low             | Send    | 0 | 0 | 0 | 1    | 0  | 0   | 0 | 0 |                                                                                                        |

The Digital8 module supports both the standard <u>shared commands</u> and the <u>shared interrupt commands</u> in addition to the following commands:

|                                  | Receive | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Return low order 5–bits of the outputs <i>00000</i>                             |

|----------------------------------|---------|---|---|---|---|---|---|---|---|---------------------------------------------------------------------------------|

| Read Outputs High                | Send    | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | Return high order 5-bits of the                                                 |

|                                  | Receive | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | outputs OOOOO                                                                   |

| Set Complement<br>Mask Low       | Send    | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | Set low order 5–bits of complement mask to <i>ccccc</i>                         |

|                                  | Send    | 0 | 0 | 0 | с | с | с | с | с |                                                                                 |

| Set Complement<br>Mask High      | Send    | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | Set high order 5 bits of complement mask to CCCCC                               |

|                                  | Send    | 0 | 0 | 0 | С | С | С | С | С |                                                                                 |

| Set Direction Mask<br>Low        | Send    | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | Set low order 5-bits of direction<br>mask to <i>ddddd</i> 1=input;<br>0=output  |

|                                  | Send    | 0 | 0 | 0 | d | d | d | d | d |                                                                                 |

| Set Direction Mask<br>High       | Send    | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | Set high order 5 bits of direction<br>mask of <i>DDDDD</i> 1=input;<br>0=output |

|                                  | Send    | 0 | 0 | 0 | D | D | D | D | D |                                                                                 |

| Reset Outputs                    | Send    | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | Set all 10 bits of outputs to 0                                                 |

| Reset Everything                 | Send    | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | Reset all registers to 0 and set direction bits to 1 (input)                    |

| Set Low Mask Low                 | Send    | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | Set low order 5–bits of low mask to <i>lllll</i>                                |

|                                  | Send    | 0 | 0 | 0 | l | l | l | l | l |                                                                                 |

| Set Low Mask High                | Send    | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | Set high order 5–bits of low mask to <i>LLLLL</i>                               |

|                                  | Send    | 0 | 0 | 0 | L | L | L | L | L |                                                                                 |

| Set High Mask Low                | Send    | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | Set low order 5–bits of the high mask to <i>hhhhh</i>                           |

|                                  | Send    | 0 | 0 | 0 | h | h | h | h | h |                                                                                 |

| Set High Mask High               | Send    | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | Set high order 5 bits of the high mask to <i>HHHHH</i>                          |

|                                  | Send    | 0 | 0 | 0 | Η | Η | Η | Η | Η |                                                                                 |

| Set Raising Mask<br>Low          | Send    | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | Set low order 5–bits of the raising mask to <i>rrrrr</i>                        |

|                                  | Send    | 0 | 0 | 0 | r | r | r | r | r |                                                                                 |

| Set Raising Mask                 | Send    | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | Set high order 5 bits of the                                                    |

| High                             | Send    | 0 | 0 | 0 | R | R | R | R | R | raising mask to RRRRR                                                           |

| Set Falling Mask                 | Send    | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | Set low order 5–bits of the                                                     |

| Low                              | Send    | 0 | 0 | 0 | f | f | f | f | f | falling mask to <i>fffff</i>                                                    |

| Set Falling Mask                 | Send    | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | Set high order 5–bits of the                                                    |

| High                             | Send    | 0 | 0 | 0 | F | F | F | F | F | falling mask to FFFFF                                                           |

| Set Outputs Low                  | Send    | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | Set low order 5–bits to <i>ooooo</i>                                            |

| Set Outputs High                 | Send    | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | Set high order 5–bits to<br>00000                                               |

| Set Output Bit                   | Send    | 0 | 1 | 1 | v | b | b | b | b | Set output bit <i>bbbb</i> to <i>v</i>                                          |

| Read Interrupt Bits              | Send    | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | Return the interrupt pending bit                                                |

|                                  | Receive | 0 | 0 | 0 | 0 | 0 | 0 | е | р | <i>p</i> and the interrupt enable bit <i>e</i> .                                |

| <u>Set Interrupt</u><br>Commands | Send    | 1 | 1 | 1 | 1 | 0 | с | с | с | Set Interrupt Command ccc.                                                      |

| Shared Commands                  | Send    | 1 | 1 | 1 | 1 | 1 | с | с | с | Execute Shared Command ccc.                                                     |

# 3. Hardware

The hardware consists of a circuit schematic and a printed circuit board.

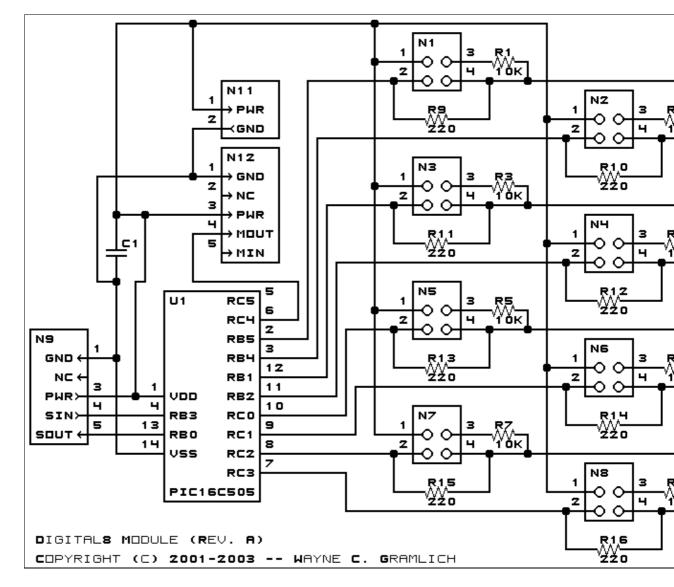

### **3.1 Circuit Schematic**

The schematic for the Digital8 module is shown below:

The parts list kept in a separate file -- <u>digital8.ptl</u>.

### **3.2 Printed Circuit Board**

The printed circuit files are listed below:

<u>digital8 back.png</u> The solder side layer. <u>digital8 front.png</u>

#### 3. Hardware

The component side layer. <u>digital8\_artwork.png</u> The artwork layer. <u>digital8.gbl</u> The RS-274X "Gerber" back (solder side) layer. <u>digital8.gtl</u> The RS-274X "Gerber" top (component side) layer. <u>digital8.gal</u> The RS-274X "Gerber" artwork layer. <u>digital8.drl</u> The "Excellon" NC drill file. <u>digital8.tol</u> The "Excellon" tool rack file.

### 4. Software

The Digital8 software is available as one of:

<u>digital8.ucl</u> The μCL source file. <u>digital8.asm</u> The resulting human readable PIC assembly file. <u>digital8.lst</u> The resulting human readable PIC listing file. <u>digital8.hex</u>

The resulting Intel<sup>®</sup> Hex file.

### 5. Issues

The following fabrication issues came up:

```

• N12 is too tight between N11 and U1.

```

```

Copyright (c) 2001–2004 by Wayne C. Gramlich. All rights reserved.

```