April 1998

LMD18245 3A, 55V DMOS Full-Bridge Motor Driver

National Semiconductor

# LMD18245 3A, 55V DMOS Full-Bridge Motor Driver

## **General Description**

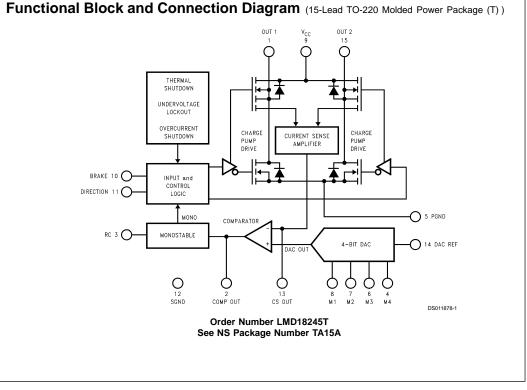

The LMD18245 full-bridge power amplifier incorporates all the circuit blocks required to drive and control current in a brushed type DC motor or one phase of a bipolar stepper motor. The multi-technology process used to build the device combines bipolar and CMOS control and protection circuitry with DMOS power switches on the same monolithic structure. The LMD18245 controls the motor current via a fixed off-time chopper technique.

An all DMOS H-bridge power stage delivers continuous output currents up to 3A (6A peak) at supply voltages up to 55V. The DMOS power switches feature low  $R_{DS(ON)}$  for high efficiency, and a diode intrinsic to the DMOS body structure eliminates the discrete diodes typically required to clamp bipolar power stages.

An innovative current sensing method eliminates the power loss associated with a sense resistor in series with the motor. A four-bit digital-to-analog converter (DAC) provides a digital path for controlling the motor current, and, by extension, simplifies implementation of full, half and microstep stepper motor drives. For higher resolution applications, an external DAC can be used.

## Features

- DMOS power stage rated at 55V and 3A continuous

- Low R<sub>DS(ON)</sub> of typically 0.3Ω per power switch

- Internal clamp diodes

- Low-loss current sensing method

- Digital or analog control of motor current

- TTL and CMOS compatible inputs

- Thermal shutdown (outputs off) at T<sub>J</sub> = 155°C

- Overcurrent protection

- No shoot-through currents

- 15-lead TO-220 molded power package

### Applications

- Full, half and microstep stepper motor drives

- Stepper motor and brushed DC motor servo drives

- Automated factory, medical and office equipment

© 1998 National Semiconductor Corporation DS011878

# Absolute Maximum Ratings (Note 1)

**BO** 1/1

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| DC Voltage at:                              |        |

|---------------------------------------------|--------|

| OUT 1, V <sub>CC</sub> , and OUT 2          | +60V   |

| COMP OUT, RC, M4, M3, M2, M1, BRAKE,        | +12V   |

| DIRECTION, CS OUT, and DAC REF              |        |

| DC Voltage PGND to SGND                     | ±400mV |

| Continuous Load Current                     | 3A     |

| Peak Load Current (Note 2)                  | 6A     |

| Junction Temperature (T <sub>J(max)</sub> ) | +150°C |

|                                             |        |

Power Dissipation (Note 3) :

$\begin{array}{ll} \text{TO-220} \ (T_{\text{A}} = 25^{\circ}\text{C}, \ \text{Infinite Heatsink}) & 25\text{W} \\ \text{TO-220} \ (T_{\text{A}} = 25^{\circ}\text{C}, \ \text{Free Air}) & 3.5\text{W} \\ \text{ESD Susceptibility (Note 4)} & 1500\text{V} \\ \text{Storage Temperature Range } (T_{\text{S}}) & -40^{\circ}\text{C} \ \text{to} \ +150^{\circ}\text{C} \\ \text{Lead Temperature (Soldering, 10 seconds)} & 300^{\circ}\text{C} \end{array}$

# **Operating Conditions** (Note 1)

| Temperature Range (T <sub>J</sub> ) (Note 3) | –40°C to +125°C |

|----------------------------------------------|-----------------|

| Supply Voltage Range (V <sub>CC</sub> )      | +12V to +55V    |

| CS OUT Voltage Range                         | 0V to +5V       |

| DAC REF Voltage Range                        | 0V to +5V       |

| MONOSTABLE Pulse Range                       | 10 µs to 100 ms |

# Electrical Characteristics (Note 2)

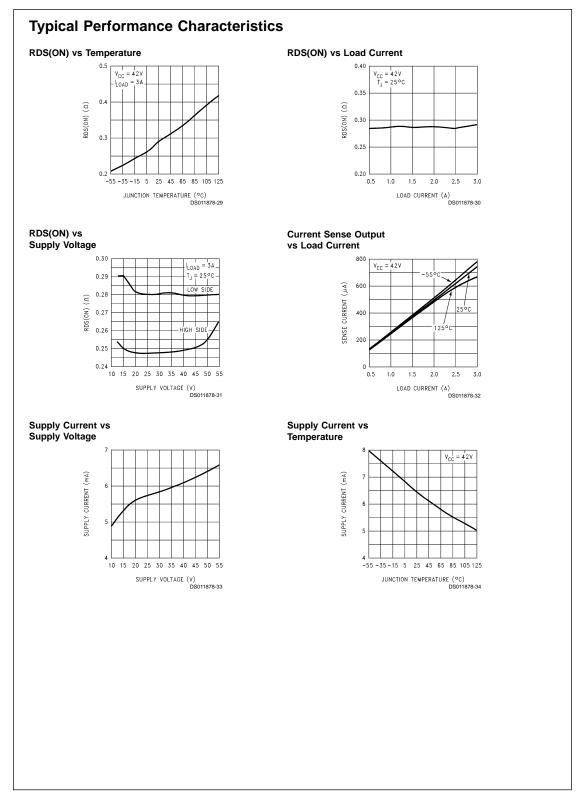

The following specifications apply for  $V_{CC} = +42V$ , unless otherwise stated. Boldface limits apply over the operating temperature range,  $-40^{\circ}C \le T_J \le +125^{\circ}C$ . All other limits apply for  $T_A = T_J = 25^{\circ}C$ .

| Symbol              | Parameter                      | Conditions                          | Typical  | Limit    | Units    |

|---------------------|--------------------------------|-------------------------------------|----------|----------|----------|

| -                   |                                |                                     | (Note 5) | (Note 5) | (Limits) |

| I <sub>cc</sub>     | Quiescent Supply Current       | DAC REF = 0V, $V_{CC}$ = +20V       | 8        |          | mA       |

|                     |                                |                                     |          | 15       | mA (max) |

| POWER O             | UTPUT STAGE                    | •                                   |          | •        |          |

| R <sub>DS(ON)</sub> | Switch ON Resistance           | I <sub>LOAD</sub> = 3A              | 0.3      | 0.4      | Ω (max)  |

|                     |                                |                                     |          | 0.6      | Ω (max)  |

|                     |                                | I <sub>LOAD</sub> = 6A              | 0.3      | 0.4      | Ω (max)  |

|                     |                                |                                     |          | 0.6      | Ω (max)  |

| V <sub>DIODE</sub>  | Body Diode Forward Voltage     | I <sub>DIODE</sub> = 3A             | 1.0      |          | V        |

|                     |                                |                                     |          | 1.5      | V(max)   |

| T <sub>rr</sub>     | Diode Reverse Recovery Time    | I <sub>DIODE</sub> = 1A             | 80       |          | ns       |

| Q <sub>rr</sub>     | Diode Reverse Recovery Charge  | I <sub>DIODE</sub> = 1A             | 40       |          | nC       |

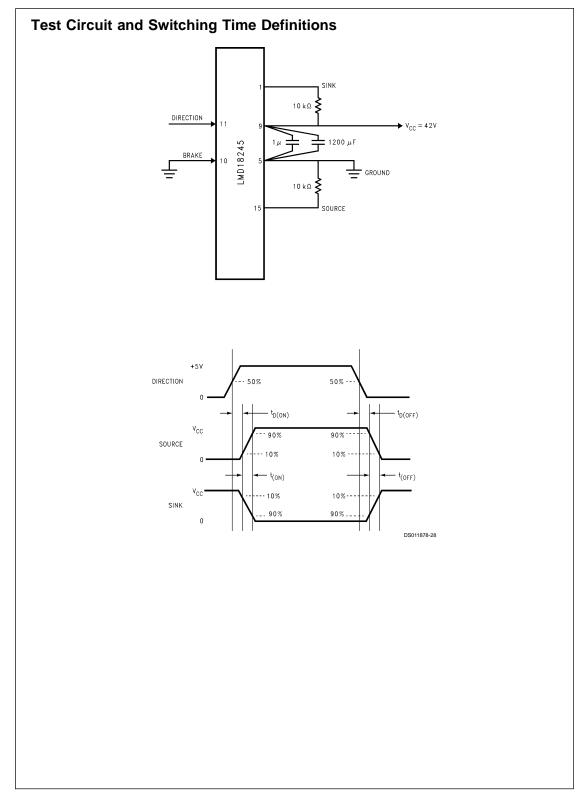

| t <sub>D(ON)</sub>  | Output Turn ON Delay Time      |                                     |          |          |          |

|                     | Sourcing Outputs               | $I_{LOAD} = 3A$                     | 5        |          | μs       |

|                     | Sinking Outputs                | I <sub>LOAD</sub> = 3A              | 900      |          | ns       |

| t <sub>D(OFF)</sub> | Output Turn OFF Delay Time     |                                     |          |          |          |

|                     | Sourcing Outputs               | I <sub>LOAD</sub> = 3A              | 600      |          | ns       |

|                     | Sinking Outputs                | $I_{LOAD} = 3A$                     | 400      |          | ns       |

| t <sub>on</sub>     | Output Turn ON Switching Time  |                                     |          |          |          |

|                     | Sourcing Outputs               | I <sub>LOAD</sub> = 3A              | 40       |          | μs       |

|                     | Sinking Outputs                | I <sub>LOAD</sub> = 3A              | 1        |          | μs       |

| t <sub>OFF</sub>    | Output Turn OFF Switching Time |                                     |          |          |          |

|                     | Sourcing Outputs               | $I_{LOAD} = 3A$                     | 200      |          | ns       |

|                     | Sinking Outputs                | I <sub>LOAD</sub> = 3A              | 80       |          | ns       |

| t <sub>pw</sub>     | Minimum Input Pulse Width      | Pins 10 and 11                      | 2        |          | μs       |

| t <sub>DB</sub>     | Minimum Dead Band              | (Note 6)                            | 40       |          | ns       |

| CURRENT             | SENSE AMPLIFIER                | •                                   | ·        |          |          |

|                     | Current Sense Output           | I <sub>LOAD</sub> = 1A (Note 7)     |          | 200      | μA (min) |

|                     |                                |                                     | 250      | 175      | μA (min) |

|                     |                                |                                     |          | 300      | μA (max) |

|                     |                                |                                     |          | 325      | µA (max) |

|                     | Current Sense Linearity Error  | $0.5A \le I_{LOAD} \le 3A$ (Note 7) | ±6       |          | %        |

|                     |                                |                                     |          | ±9       | %(max)   |

|                     | Current Sense Offset           | $I_{LOAD} = 0A$                     | 5        |          | μA       |

|                     |                                |                                     |          | 20       | µA (max) |

|                  | Parameter                             | Conditions                  | Typical  | Limit    | Units     |

|------------------|---------------------------------------|-----------------------------|----------|----------|-----------|

| DIGITAI -T       |                                       |                             | (Note 5) | (Note 5) | (Limits)  |

|                  | O-ANALOG CONVERTER (DAC)              |                             |          |          |           |

|                  | Resolution                            |                             |          | 4        | Bits (min |

|                  | Monotonicity                          |                             |          | 4        | Bits (min |

|                  | Total Unadjusted Error                |                             | 0.125    | 0.25     | LSB (max  |

|                  |                                       |                             |          | 0.5      | LSB (max  |

|                  | Propagation Delay                     |                             | 50       |          | ns        |

| I <sub>REF</sub> | DAC REF Input Current                 | DAC REF = +5V               | -0.5     |          | μA        |

|                  |                                       |                             |          | ±10      | μA (max   |

| COMPARA          | TOR AND MONOSTABLE                    |                             |          |          |           |

|                  | Comparator High Output Level          |                             | 6.27     |          | V         |

|                  | Comparator Low Output Level           |                             | 88       |          | mV        |

|                  | Comparator Output Current             |                             |          |          |           |

|                  | Source                                |                             | 0.2      |          | mA        |

|                  | Sink                                  |                             | 3.2      |          | mA        |

|                  | Monostable Turn OFF Delay             | (Note 8)                    | 1.2      |          | μs        |

|                  |                                       |                             |          | 2.0      | µs (max   |

| PROTECTI         | ION AND PACKAGE THERMAL RE            | SISTANCES                   |          |          |           |

|                  | Undervoltage Lockout, V <sub>CC</sub> |                             |          | 5        | V (min)   |

|                  |                                       |                             |          | 8        | V (max)   |

| T <sub>JSD</sub> | Shutdown Temperature, T <sub>J</sub>  |                             | 155      |          | °C        |

|                  | Package Thermal Resistances           |                             |          |          |           |

| θ <sub>JC</sub>  | Junction-to-Case, TO-220              |                             | 1.5      |          | °C/W      |

| θ.ιΑ             | Junction-to-Ambient, TO-220           |                             | 35       |          | °C/W      |

| LOGIC INF        | PUTS                                  | 1                           | 1        |          |           |

| VII              | Low Level Input Voltage               |                             |          | -0.1     | V (min)   |

|                  |                                       |                             |          | 0.8      | V (max)   |

| V <sub>IH</sub>  | High Level Input Voltage              |                             |          | 2        | V (min)   |

|                  |                                       |                             |          | 12       | V (max)   |

| I <sub>IN</sub>  | Input Current                         | V <sub>IN</sub> = 0V or 12V |          | ±10      | µA (max   |

Note 7: (ILOAD, ISENSE) data points are taken for load currents of 0.5A, 1A, 2A and 3A. The current sense gain is specified as ISENSE/LOAD for the 1A data point. The current sense linearity is specified as the slope of the line between the 0.5A and 1A data points minus the slope of the line between the 2A and 3A data points all divided by the slope of the line between the 0.5A and 1A data points.

Note 8: Turn OFF delay,  $t_{DELAY}$ , is defined as the time from the voltage at the output of the current sense amplifier reaching the DAC output voltage to the lower DMOS switch beginning to turn OFF. With V<sub>CC</sub> = 32V, DIRECTION high, and 200 $\Omega$  connected between OUT1 and V<sub>CC</sub>, the voltage at RC is increased from 0V to 5V at 1.2V/µs, and  $t_{DELAY}$  is measured as the time from the voltage at RC reaching 2V to the time the voltage at OUT 1 reaches 3V.

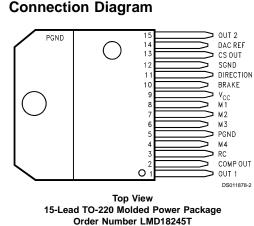

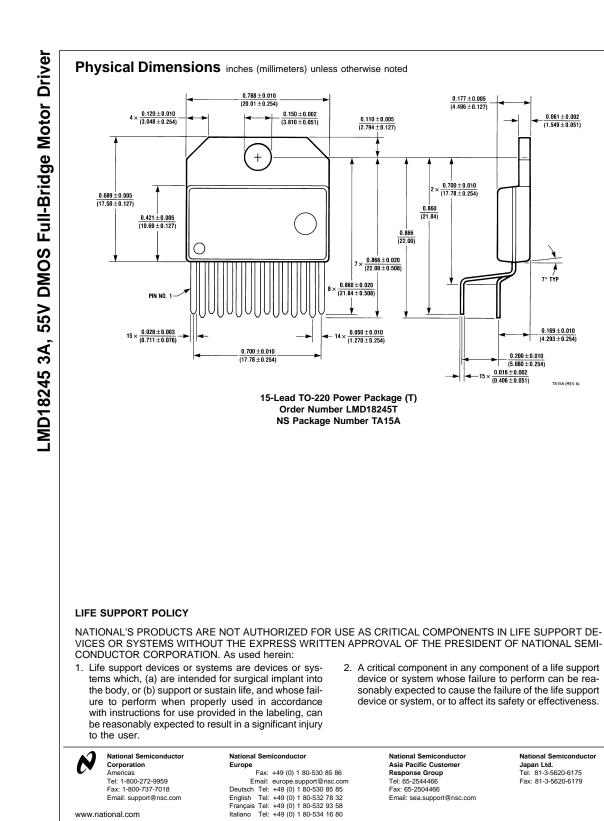

#### See NS Package Number TA15A

**Pinout Descriptions** (See Functional Block and Connection Diagrams)

Pin 1, OUT 1: Output node of the first half H-bridge.

**Pin 2, COMP OUT:** Output of the comparator. If the voltage at CS OUT exceeds that provided by the DAC, the comparator triggers the monostable.

**Pin 3, RC:** Monostable timing node. A parallel resistorcapacitor network connected between this node and ground sets the monostable timing pulse at about 1.1 RC seconds.

**Pin 5, PGND:** Ground return node of the power bridge. Bond wires (internal) connect PGND to the tab of the TO-220 package.

**Pins 4 and 6 through 8, M4 through M1:** Digital inputs of the DAC. These inputs make up a four-bit binary number with M4 as the most significant bit or MSB. The DAC provides an analog voltage directly proportional to the binary number applied at M4 through M1.

Pin 9, V<sub>CC</sub>: Power supply node.

**Pin 10, BRAKE:** Brake logic input. Pulling the BRAKE input logic-high activates both sourcing switches of the power bridge — effectively shorting the load. See *Table 1*. Shorting the load in this manner forces the load current to recirculate and decay to zero.

**Pin 11, DIRECTION:** Direction logic input. The logic level at this input dictates the direction of current flow in the load. See *Table 1*.

Pin 12, SGND: Ground return node of all signal level circuits.

**Pin 13, CS OUT:** Output of the current sense amplifier. The current sense amplifier sources  $250 \ \mu A$  (typical) per ampere of total forward current conducted by the upper two switches of the power bridge.

**Pin 14, DAC REF:** Voltage reference input of the DAC. The DAC provides an analog voltage equal to  $V_{DAC REF} \times D/16$ , where D is the decimal equivalent (0–15) of the binary number applied at M4 through M1.

Pin 15, OUT 2: Output node of the second half H-bridge.

| TABLE 1. Switch | Control | Logic | Truth | Table |

|-----------------|---------|-------|-------|-------|

|-----------------|---------|-------|-------|-------|

| BRAKE          | DIRECTION | MONO | Active Switches    |  |  |

|----------------|-----------|------|--------------------|--|--|

| н              | Х         | Х    | Source 1, Source 2 |  |  |

| L              | Н         | L    | Source 2           |  |  |

| L              | Н         | Н    | Source 2, Sink 1   |  |  |

| L              | L         | L    | Source 1           |  |  |

| L              | L         | Н    | Source 1, Sink 2   |  |  |

| X = don't care |           |      |                    |  |  |

MONO is the output of the monostable

## **Functional Descriptions**

### TYPICAL OPERATION OF A CHOPPER AMPLIFIER

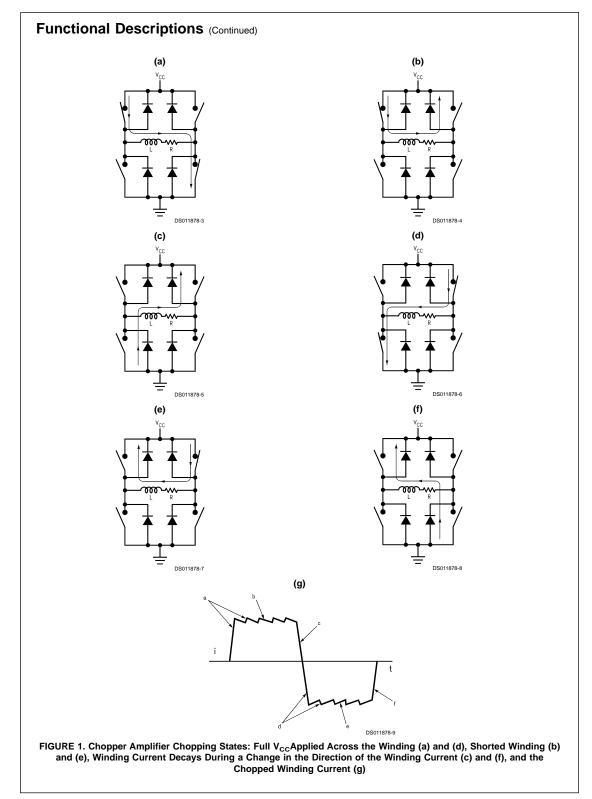

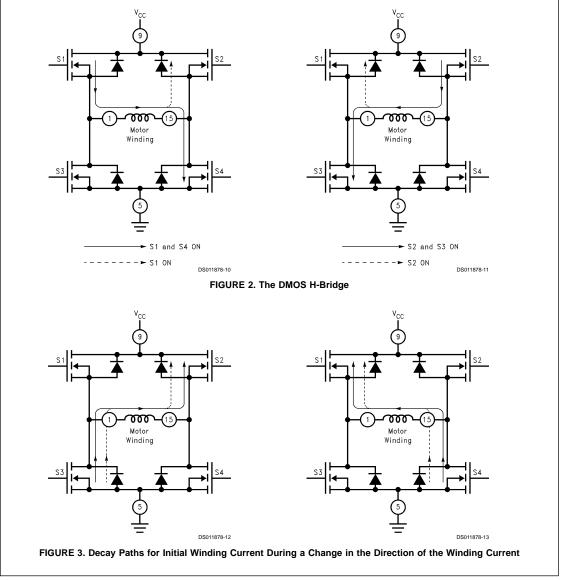

Chopper amplifiers employ feedback driven switching of a power bridge to control and limit current in the winding of a motor (Figure 1). The bridge consists of four solid state power switches and four diodes connected in an H configuration. Control circuitry (not shown) monitors the winding current and compares it to a threshold. While the winding current remains less than the threshold, a source switch and a sink switch in opposite halves of the bridge force the supply voltage across the winding, and the winding current increases rapidly towards  $V_{\rm CC}/R$  (Figure 1a and Figure 1d). As the winding current surpasses the threshold, the control circuitry turns OFF the sink switch for a fixed period or off-time. During the off-time, the source switch and the opposite upper diode short the winding, and the winding current recirculates and decays slowly towards zero (Figure 1b and Figure 1e). At the end of the off-time, the control circuitry turns back ON the sink switch, and the winding current again increases rapidly towards V<sub>CC</sub>/R (Figure 1a and Figure 1d again). The above sequence repeats to provide a current chopping action that limits the winding current to the threshold (Figure 1g). Chopping only occurs if the winding current reaches the threshold. During a change in the direction of the winding current, the diodes provide a decay path for the initial winding current (Figure 1c and Figure 1f). Since the bridge shorts the winding for a fixed period, this type of chopper amplifier is commonly referred to as a fixed off-time chopper.

# Functional Descriptions (Continued)

### THE LMD18245 CHOPPER AMPLIFIER

The LMD18245 incorporates all the circuit blocks needed to implement a fixed off-time chopper amplifier. These blocks include: an all DMOS, full H-bridge with clamp diodes, an amplifier for sensing the load current, a comparator, a monostable, and a DAC for digital control of the chopping threshold. Also incorporated are logic, level shifting and drive blocks for digital control of the direction of the load current and braking.

#### THE H-BRIDGE

The power stage consists of four DMOS power switches and associated body diodes connected in an H-bridge configuration (*Figure 2*). Turning ON a source switch and a sink switch in opposite halves of the bridge forces the full supply voltage less the switch drops across the motor winding. While the bridge remains in this state, the winding current increases exponentially towards a limit dictated by the supply voltage, the switch drops, and the winding resistance. Subsequently turning OFF the sink switch causes a voltage transient that forward biases the body diode of the other source switch. The diode clamps the transient at one diode drop above the supply voltage and provides an alternative current path. While the bridge remains in this state, it essentially shorts the winding and the winding current recirculates and decays exponentially towards zero. During a change in the bidge provide a decay path for the initial winding current (*Figure 3*).

# Functional Descriptions (Continued)

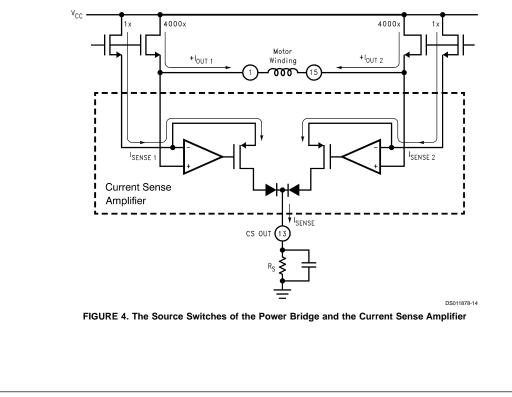

#### THE CURRENT SENSE AMPLIFIER

Many transistor cells in parallel make up the DMOS power switches. The current sense amplifier (*Figure 4*) uses a small fraction of the cells of both upper switches to provide a unique, low-loss means for sensing the load current. In practice, each upper switch functions as a 1x sense device in parallel with a 4000x power device. The current sense amplifier forces the voltage at the source of the sense device to equal that at the source of the power device; thus, the devices share the total drain current in proportion to the 1:4000 cell ratio. Only the current flowing from drain to source, the forward current, registers at the output of the current sense amplifier. The current sense amplifier, therefore, sources 250  $\mu$ A per ampere of total forward current conducted by the upper two switches of the power bridge.

The sense current develops a potential across  $R_{\rm S}$ that is proportional to the load current; for example, per ampere of load current, the sense current develops one volt across a 4 k\Omega resistor (the product of 250  $\mu A$  per ampere and 4 k $\Omega$ ). Since chopping of the load current occurs as the voltage at CS OUT surpasses the threshold (the DAC output voltage),  $R_{\rm S}$  sets the gain of the chopper amplifier; for example, a 2 k\Omega resistor sets the gain at two amperes of load current per volt of the threshold (the reciprocal of the product of 250  $\mu A$  per ampere and 2 k $\Omega$ ). A quarter watt resistor suffices. A low value capacitor connected in parallel with  $R_{\rm S}$  filters the effects of switching noise from the current sense signal.

While the specified maximum DC voltage compliance at CS OUT is 12V, the specified operating voltage range at CS OUT is 0V to 5V.

#### THE DIGITAL-TO-ANALOG CONVERTER (DAC)

The DAC sets the threshold voltage for chopping at  $V_{DAC\ REF} x D/16$ , where D is the decimal equivalent (0–15) of the binary number applied at M4 through M1, the digital inputs of the DAC. M4 is the MSB or most significant bit. For applications that require higher resolution, an external DAC can drive the DAC REF input. While the specified maximum DC voltage compliance at DAC REF is 12V, the specified operating voltage range at DAC REF is 0V to 5V.

# THE COMPARATOR, MONOSTABLE AND WINDING CURRENT THRESHOLD FOR CHOPPING

As the voltage at CS OUT surpasses that at the output of the DAC, the comparator triggers the monostable, and the monostable, once triggered, provides a timing pulse to the control logic. During the timing pulse, the power bridge shorts the motor winding, causing current in the winding to recirculate and decay slowly towards zero (*Figure 1b* and *Figure 1e* again). A parallel resistor-capacitor network connected between RC (pin #3) and ground sets the timing pulse or off-time at about 1.1 RC seconds.

Chopping of the winding current occurs as the voltage at CS OUT exceeds that at the output of the DAC; so chopping occurs at a winding current threshold of about

(V\_DAC REF x D/16)  $\div$  ((250 x 10^{-6}) x R\_S)) amperes.

## **Applications Information** POWER SUPPLY BYPASSING

Step changes in current drawn from the power supply occur repeatedly during normal operation and may cause large voltage spikes across inductance in the power supply line. Care must be taken to limit voltage spikes at  $V_{CC}$  to less than the 60V Absolute Maximum Rating. At a change in the direction of the load current, the initial load current tends to raise the voltage at the power supply rail (Figure 3) again. Current transients caused by the reverse recovery of the clamp diodes tend to pull down the voltage at the power supply rail. Bypassing the power supply line at  $V_{CC}$  is required to protect the device and minimize the adverse effects of normal operation on the power supply rail. Using both a 1 µF high frequency ceramic capacitor and a large-value aluminum electrolytic capacitor is highly recommended. A value of 100 µF per ampere of load current usually suffices for the aluminum electrolytic capacitor. Both capacitors should have short

#### OVERCURRENT PROTECTION

leads and be located within one half inch of  $V_{CC}$ .

If the forward current in either source switch exceeds a 12A threshold, internal circuitry disables both source switches, forcing a rapid decay of the fault current (Figure 5). Approximately 3 us after the fault current reaches zero, the device restarts. Automatic restart allows an immediate return to normal operation once the fault condition has been removed. If the fault persists, the device will begin cycling into and out of thermal shutdown. Switching large fault currents may cause potentially destructive voltage spikes across inductance in the power supply line; therefore, the power supply line must be properly bypassed at  $V_{\rm CC}$  for the motor driver to survive an extended overcurrent fault.

In the case of a locked rotor, the inductance of the winding tends to limit the rate of change of the fault current to a value easily handled by the protection circuitry. In the case of a low inductance short from either output to ground or between outputs, the fault current could surge past the 12A shutdown threshold, forcing the device to dissipate a substantial amount of power for the brief period required to disable the source switches. Because the fault power must be dissipated by only one source switch, a short from output to ground represents the worst case fault. Any overcurrent fault is potentially destructive, especially while operating with high supply voltages (≥30V), so precautions are in order. Sinking V<sub>CC</sub> for heat with 1 square inch of 1 ounce copper on the printed circuit board is highly recommended. The sink switches are not internally protected against shorts to  $V_{CC}$ .

### THERMAL SHUTDOWN

Internal circuitry senses the junction temperature near the power bridge and disables the bridge if the junction temperature exceeds about 155°C. When the junction temperature cools past the shutdown threshold (lowered by a slight hysteresis), the device automatically restarts.

#### UNDERVOLTAGE LOCKOUT

Internal circuitry disables the power bridge if the power supply voltage drops below a rough threshold between 8V and 5V. Should the power supply voltage then exceed the threshold, the device automatically restarts.

Trace: Fault Current at 5A/div Horizontal: 20 us/div

FIGURE 5. Fault Current with V<sub>CC</sub> = 30V, OUT 1 Shorted to OUT 2, and CS OUT Grounded

# The Typical Application

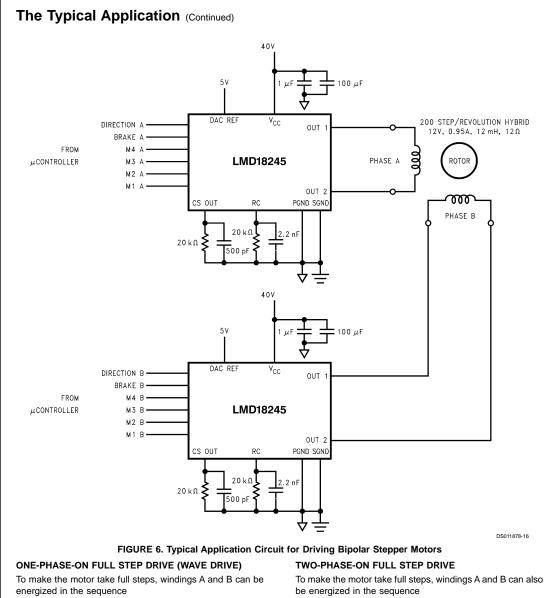

Figure 6 shows the typical application, the power stage of a chopper drive for bipolar stepper motors. The 20  $k\Omega$  resistor and 2.2 nF capacitor connected between RC and ground set the off-time at about 48  $\mu s,$  and the 20 k $\Omega$  resistor connected between CS OUT and ground sets the gain at about 200 mA per volt of the threshold for chopping. Digital signals control the thresholds for chopping, the directions of the winding currents, and, by extension, the drive type (full step, half step, etc.). A µprocessor or µcontroller usually provides the digital control signals.

$A{\rightarrow}B{\rightarrow}A^*{\rightarrow}B^*{\rightarrow}A{\rightarrow}...,$

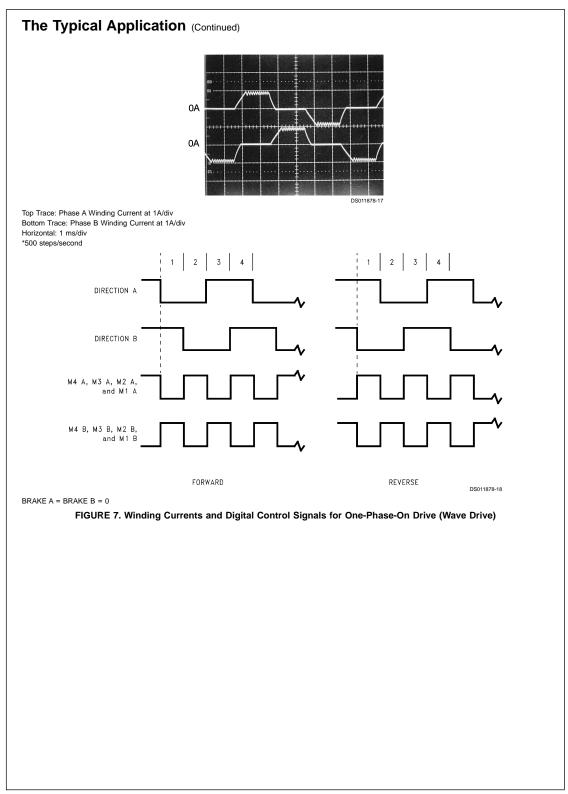

where A represents winding A energized with current in one direction and A\* represents winding A energized with current in the opposite direction. The motor takes one full step each time one winding is de-energized and the other is energized. To make the motor step in the opposite direction, the order of the above sequence must be reversed. *Figure 7* shows the winding currents and digital control signals for a wave drive application of the typical application circuit.

be energized in the sequence  $AB \rightarrow A^*B \rightarrow A^*B^* \rightarrow AB^* \rightarrow AB \rightarrow ...,$ and because both windings are energized at all times, this

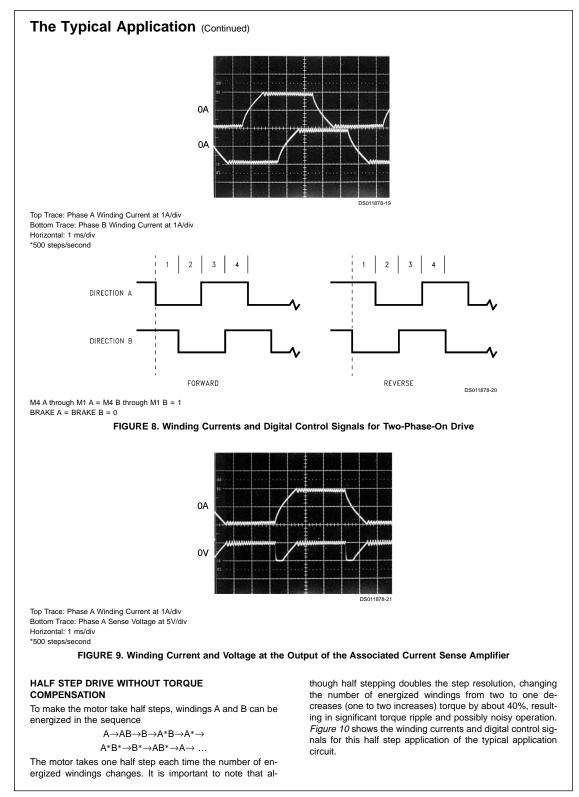

and because both windings are energized at all times, this sequence produces more torque than that produced with wave drive. The motor takes one full step at each change of direction of either winding current. *Figure 8* shows the winding currents and digital control signals for this application of the typical application circuit, and *Figure 9* shows, for a single phase, the winding current and voltage at the output of the associated current sense amplifier.

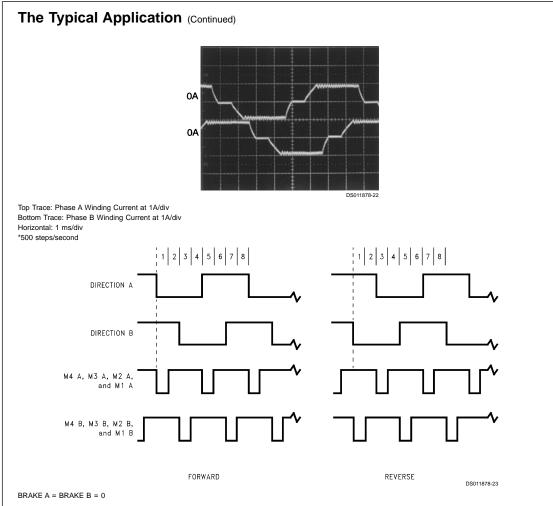

#### FIGURE 10. Winding Currents and Digital Control Signals for Half Step Drive without Torque Compensation

#### HALF STEP DRIVE WITH TORQUE COMPENSATION

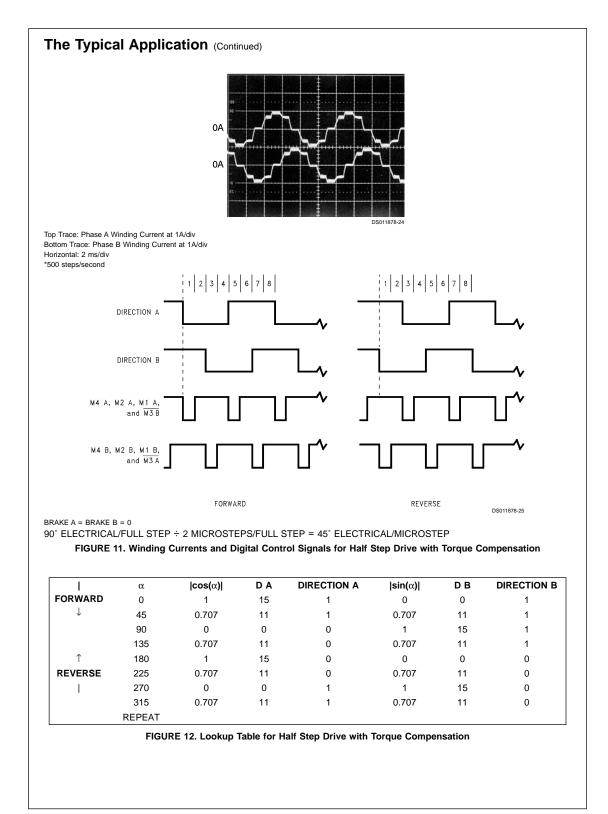

To make the motor take half steps, the windings can also be energized with sinusoidal currents (*Figure 11*). Controlling the winding currents in the fashion shown doubles the step resolution without the significant torque ripple of the prior drive technique. The motor takes one half step each time the level of either winding current changes. Half step drive with torque compensation is microstepping drive. Along with the obvious advantage of increased step resolution, microstepping reduces both full step oscillations and resonances that occur as the motor and load combination is driven at its natural resonant frequency or subharmonics thereof. Both of these advantages are obtained by replacing full steps with bursts of microsteps. When compared to full step drive, the motor runs smoother and quieter.

*Figure 12* shows the lookup table for this application of the typical application circuit. Dividing 90°electrical per full step by two microsteps per full step yields 45° electrical per microstep.  $\alpha$ , therefore, increases from 0 to 315° in increments of 45°. Each full 360° cycle comprises eight half steps. Rounding  $|\cos\alpha|$  to four bits gives D A, the decimal equivalent of the binary number applied at M4 A through M1 A. DI-RECTION A controls the polarity of the current in winding A. *Figure 11* shows the sinusoidal winding currents.

# The Typical Application (Continued)

## QUARTER STEP DRIVE WITH TORQUE COMPENSATION

Figure 13 shows the winding currents and lookup table for a quarter step drive (four microsteps per full step) with torque compensation.

Top Trace: Phase A Winding Current at 1A/div Bottom Trace: Phase B Winding Current at 1A/div

Horizontal: 2ms/div

\*250 steps/second

90° ELECTRICAL/FULL STEP ÷ 4 MICROSTEPS/FULL STEP = 22.5° ELECTRICAL/MICROSTEP

|              | α      | cos(α) | DA | DIRECTION A | sin(α) | DВ | DIRECTION B |

|--------------|--------|--------|----|-------------|--------|----|-------------|

|              | 0      | 1      | 15 | 1           | 0      | 0  | 1           |

|              | 22.5   | 0.924  | 14 | 1           | 0.383  | 6  | 1           |

| I            | 45     | 0.707  | 11 | 1           | 0.707  | 11 | 1           |

| FORWARD      | 67.5   | 0.383  | 6  | 1           | 0.924  | 14 | 1           |

| $\downarrow$ | 90     | 0      | 0  | 0           | 1      | 15 | 1           |

|              | 112.5  | 0.383  | 6  | 0           | 0.924  | 14 | 1           |

| $\uparrow$   | 135    | 0.707  | 11 | 0           | 0.707  | 11 | 1           |

| REVERSE      | 157.5  | 0.924  | 14 | 0           | 0.383  | 6  | 1           |

| I            | 180    | 1      | 15 | 0           | 0      | 0  | 0           |

|              | 202.5  | 0.924  | 14 | 0           | 0.383  | 6  | 0           |

|              | 225    | 0.707  | 11 | 0           | 0.707  | 11 | 0           |

|              | 247.5  | 0.383  | 6  | 0           | 0.924  | 14 | 0           |

|              | 270    | 0      | 0  | 1           | 1      | 15 | 0           |

|              | 292.5  | 0.383  | 6  | 1           | 0.924  | 14 | 0           |

|              | 315    | 0.707  | 11 | 1           | 0.707  | 11 | 0           |

|              | 337.5  | 0.924  | 14 | 1           | 0.383  | 6  | 0           |

|              | REPEAT |        |    |             |        |    |             |

BRAKE A = BRAKE B = 0

FIGURE 13. Winding Currents and Lookup Table for Quarter Step Drive with Torque Compensation

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.